Inverter input voltage margin

Interpreting inverter datasheet and main parameters | AE 868

Both the maximum voltage value and operating voltage range of an inverter are two main parameters that should be taken into account when stringing the inverter and PV array. PV

Microsoft PowerPoint

Layout the inverter using the Mentor tools, extract parasitics, and simulate the extracted circuit on HSPICE t o mak e sure th at your d esi gn conf orms t o th e specifi ifi cati on. Do the same

PowerPoint Presentation

CMOS Inverter: DC Analysis Analyze DC Characteristics of CMOS Gates by studying an Inverter DC Analysis DC value of a signal in static conditions DC Analysis of CMOS Inverter Vin, input

Exploring the Cmos Inverter Circuit: A Schematic

The noise margin is important because it ensures that the inverter can tolerate noise or variations in the input voltage without causing incorrect logic

Inverter Specifications and Data Sheet

The article provides an overview of inverter functions, key specifications, and common features found in inverter systems, along with an example of power

Understanding inverter voltage

For a 12V inverter, the maximum input inverter voltage is typically around 16VDC. This safety margin provides a buffer to accommodate fluctuations in the power source and

EEC 118 Lecture #4: CMOS Inverters

V OH and V OL represent the "high" and "low" output voltages of the inverter V = output voltage when OH Vin = ''0'' (V Output High) V = output voltage when OL Vin = ''1'' (V Output Low)

Noise margin explained

Noise margin explained In electrical engineering, noise margin is the maximum voltage amplitude of extraneous signal that can be algebraically added to the noise-free worst-case input level

Microsoft PowerPoint

3 V 2 V DD th 8 3 : noise margin for high input NM L: noise margin for low input Vth: threshold voltage Noise margins are typically around 0.4 VDD; close to half power-supply voltage CMOS

ELEC 2020 EXPERIMENT 11

An inverter circuit outputs a voltage representing the opposite logic-level to its input. Inverters can be constructed using a single NMOS transistor or a single PMOS transistor coupled with a

Microsoft Word

Thus, VOH is essentially the "ideal" inverter high output, as it is the output voltage when the inverter input is at its ideal low input value vI=0. Typically, VOH is a value just slightly less than

CMOS Inverter Characteristics | Tutorials on Electronics | Next

Diagram Description: The diagram would show the physical arrangement of the CMOS inverter, including the PMOS and NMOS transistors, their connections to the power supply and ground,

Unit 2 MOS Inverters

Both these voltages play significant roles in determining the Noise Margins of inverter circuits. As the input voltage is further increased, the output voltage continues to drop and reaches a value

Microsoft PowerPoint

Noise margin is a measure o f th e ro b ust ness o f an inverter N ML = V IL - V OL N = V - V MH OH IH Models a chain of inverters. Example: First inverter output is V OH Second inverter

EE414 Lecture Notes (electronic)

VIL is the input low voltage which corresponds to an output high voltage with a slope of -1. the most common type of inverter in VLSI is CMOS. This is due to the low static power

Inverter Battery Voltage Chart

An inverter battery voltage chart shows the relationship between a battery''s charge level and its voltage. Battery voltage charts describe the relation between the battery''s charge

Microsoft Word

The input vI2=VOL is typically well below the maximum acceptable value VIL. In fact, we have a specific name for the difference between VIL and VOL—we call this value Noise Margin (NM):

Related information

- The relationship between energy storage and energy in Colombia

- Macedonia outdoor power supply installation

- Moldova Electric Power Energy Base Station

- Zambia energy storage low temperature lithium battery factory

- Valley Power Energy Storage and Solar Energy Applications

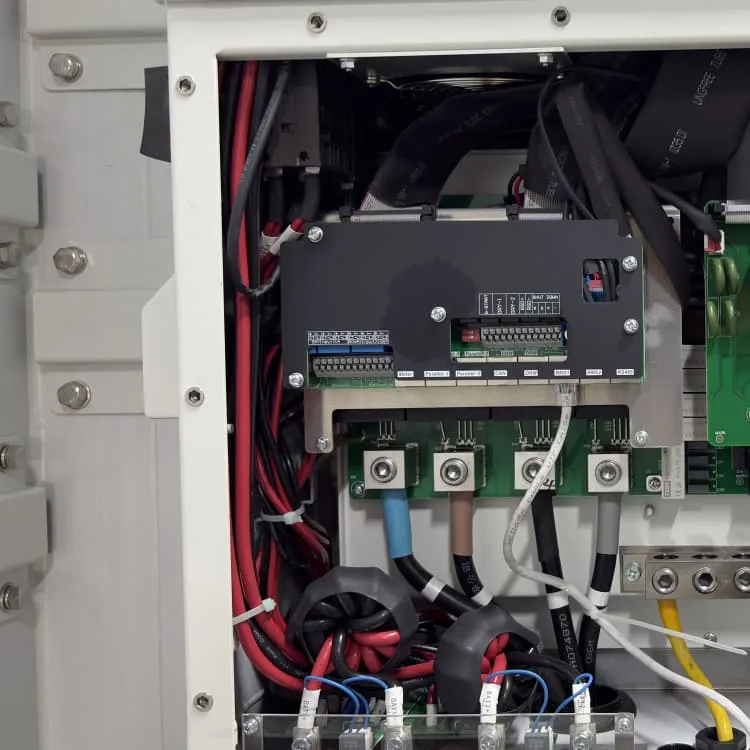

- Côte d Ivoire Communication Base Station Inverter Grid-Connected Infrastructure Project

- Kyrgyzstan Simple House Energy Storage Battery

- What size inverter is suitable for 48v 12ah

- Actual application scenarios of energy storage batteries

- How many kilowatt-hours of electricity does a 1 megawatt solar panel generate per hour

- Photovoltaic solar panel waste heat utilization

- Can photovoltaic panels be directly connected to the inverter

- Specifications of outdoor solar integrated machine

- Solar energy and energy storage cabinet system

- Venezuela communication base station inverter grid connection

- Side energy storage grid business model

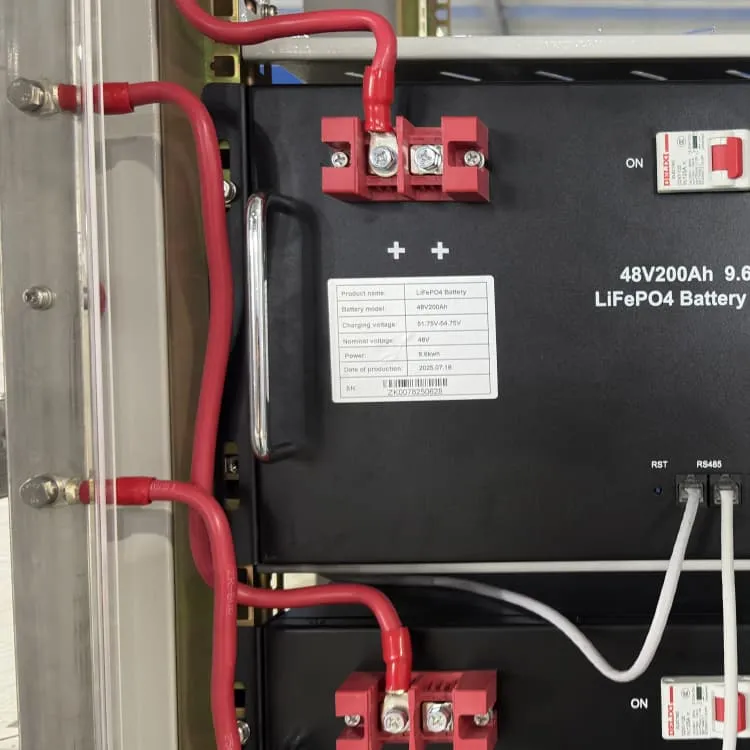

- Dongya lithium iron phosphate energy storage battery cabinet

- South African container energy storage plant

- Which companies are suitable for using energy storage batteries

- Photovoltaic panels and cells

- How to choose solar energy outdoor site

- The current generated by 22 photovoltaic panels

- Efficiency of a photovoltaic panel